台积电引领未来堆叠芯片封装技术的革新之路

在半导体行业的快速发展中,台积电(TSMC)始终处于技术创新的前沿。近年来,随着对更高性能和更低功耗的需求日益增长,堆叠芯片封装技术成为了行业内的一大热点。台积电在这一领域的探索和实践,不仅推动了自身技术的进步,也对整个半导体产业产生了深远的影响。

1. 堆叠芯片封装技术概述

堆叠芯片封装技术,也称为3D封装或3D集成电路,是一种将多个芯片垂直堆叠在一起,并通过硅通孔(TSV)技术实现芯片间的高速通信和数据传输的技术。这种技术可以显著提高芯片的集成度和性能,同时减少能耗和物理空间的需求。

2. 台积电在堆叠芯片封装技术上的创新

台积电在堆叠芯片封装技术上的研究和开发主要集中在几个关键领域:

CoWoS(Chip on Wafer on Substrate)技术

:这是一种将逻辑芯片和存储芯片集成在同一封装中的技术。台积电通过优化设计和制造流程,提高了CoWoS技术的性能和可靠性,使其成为高性能计算和数据中心应用的理想选择。

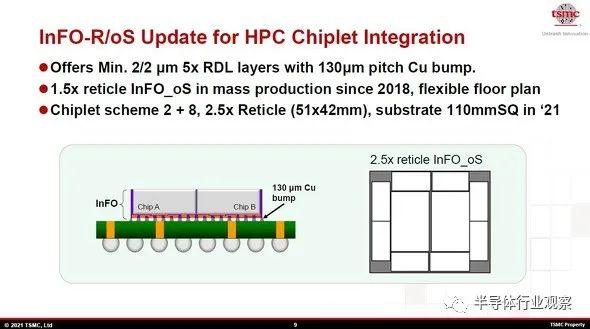

InFO(Integrated FanOut)技术

:InFO技术利用扇出封装的优势,可以在没有基板的情况下实现芯片的堆叠和封装。这种技术特别适合移动设备和消费电子产品,因为它可以减少封装厚度,提高信号传输速度。

3D Fabric技术

:台积电推出的3D Fabric技术整合了前端3D芯片堆叠和后端3D封装技术,提供了从设计到制造的全方位解决方案。这一技术的推出,标志着台积电在3D集成电路领域的全面领先。3. 技术挑战与解决方案

尽管堆叠芯片封装技术带来了许多优势,但在实际应用中也面临着诸多挑战,如热管理、信号完整性和成本控制等。台积电通过持续的研发投入,不断优化材料、设计和制造工艺,有效解决了这些问题。

热管理

:随着芯片堆叠层数的增加,热量的积累成为一个严重问题。台积电开发了高效的热传导材料和设计,确保了芯片在高负载下的稳定运行。

信号完整性

:在3D封装中,信号传输路径的复杂性增加,可能导致信号衰减和干扰。台积电通过精确的布线和信号优化技术,保证了高速数据传输的可靠性。

成本控制

:堆叠芯片封装技术的成本相对较高,台积电通过规模化生产和工艺优化,有效降低了成本,使得这一技术更加普及。4. 未来展望

随着人工智能、5G通信和物联网等技术的快速发展,对高性能、低功耗芯片的需求将持续增长。台积电在堆叠芯片封装技术上的持续创新,将为其在未来的市场竞争中保持领先地位提供强大支持。预计未来几年,台积电将继续扩大其在3D封装技术领域的研发投入,推动更多创新产品的问世。

5. 结语

台积电在堆叠芯片封装技术上的探索和成就,不仅展示了其在半导体制造领域的技术实力,也为整个行业的发展指明了方向。随着技术的不断进步,我们有理由相信,台积电将继续引领半导体技术的新潮流,为全球的科技进步和产业升级做出更大的贡献。